Logic Observer

Mar 4th, 2015 by Alex

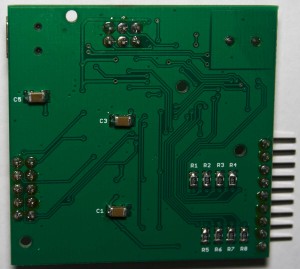

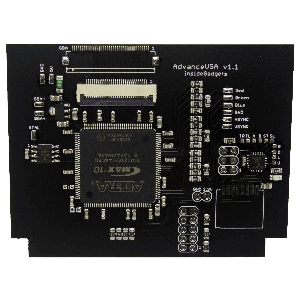

An 8 input CPLD based Logic Analyser with a selectable sample rate up to 50 MSPS with up to 131Kbit sample depth per input, controllable via USB with a GUI or command line interface and data format readable by Sigrok PulseView.

Features

- 2V to 5.5V input voltage for logic high reading

- 4.7M input impedance

- Sample rate of 50/10/5/2.5/1 MSPS and 500/250/100 KSPS

- Sample depth of 8K, 16K, 32K, 64K, 96K or 131K

- Selectable trigger pins

- High/low voltage triggering

- Trigger delay of 0 to 254ms

- Trigger count of 0 to 254 times

- Ability to re-program Altera CPLD / Atmel MCU

Specs

- PCB Board: 50mm x 50mm

- Minimum input voltage: -0.5V

- Maximum input voltage: 5.5V

- Weight: 15 grams

- CPLD: Altera 64 macro cell EPM3064ATC44

- MCU: Atmel ATmega48/88/168/328 QFP

- SRAM: Cypress 1Mbit SRAM CY7C1019DV33

Download

Includes schematic, manual, example results, product pictures, PCB guide, source and program.

View the manual – Logic_Observer_v1.0_Manual_Rev2

v1.0 Rev 2 (26 April 2015) – Logic_Observer_v1.0_Rev2

– Added pin state change detection in pin change interrupt so it only counts as a trigger if the pin has changed state.

– Added initial detection of pin state so we don’t have to wait until the pin change interrupt is triggered to start capturing

– Moved clock stabilise delay to after starting a capture and waiting for a trigger as occasionally if a trigger occurred straight away, the first few readings would be random data

v1.0 (28 February 2015) – Logic_Observer_v1.0

– Initial Release

This work is licensed under a Creative Commons Attribution-NonCommercial 3.0 Unported License.